Deck 7: Counters and Registers

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Unlock Deck

Sign up to unlock the cards in this deck!

Unlock Deck

Unlock Deck

1/75

Play

Full screen (f)

Deck 7: Counters and Registers

1

A MOD- 16 ripple counter is holding the count 10112. What will the count be after 31 clock pulses?

A) 10012

B) 10102

C) 11002

D) 10112

A) 10012

B) 10102

C) 11002

D) 10112

10102

2

The primary difference between a 3- bit up- counter and a 3- bit down- counter is:

A) An up counter's output decreases by one with each input clock pulse whereas a down counter's output increases by one with each input clock pulse.

B) An up counter's output increases by one with each input clock pulse whereas a down counter's output decreases by one with each input clock pulse.

C) In a normal count sequence, a 000 is followed by 001 (in an up- counter) and by 111 (in a down- counter).

D) Both B and C

E) Both A and C

A) An up counter's output decreases by one with each input clock pulse whereas a down counter's output increases by one with each input clock pulse.

B) An up counter's output increases by one with each input clock pulse whereas a down counter's output decreases by one with each input clock pulse.

C) In a normal count sequence, a 000 is followed by 001 (in an up- counter) and by 111 (in a down- counter).

D) Both B and C

E) Both A and C

Both B and C

3

The process of designing a synchronous counter that will count in a nonbinary sequence is primarily based on:

A) modifying asynchronous counters to change states on every second input clock pulse.

B) modifying BCD counters to change states on every second input clock pulse.

C) elimination of the counter stages and the addition of combinatorial logic circuits to produce the desired counts.

D) external logic circuits that decode the various states of the counter to apply the correct logic levels to the J- K inputs.

A) modifying asynchronous counters to change states on every second input clock pulse.

B) modifying BCD counters to change states on every second input clock pulse.

C) elimination of the counter stages and the addition of combinatorial logic circuits to produce the desired counts.

D) external logic circuits that decode the various states of the counter to apply the correct logic levels to the J- K inputs.

external logic circuits that decode the various states of the counter to apply the correct logic levels to the J- K inputs.

4

An 8- bit counter is wired as follows: The CLK input to the first stage (LSB) is the system clock. Each stage's output is used as the CLK input to the next higher stage. This counter is a:

A) MOD 128 synchronous counter.

B) MOD 256 ripple counter.

C) MOD 128 ripple counter.

D) MOD 256 synchronous counter.

A) MOD 128 synchronous counter.

B) MOD 256 ripple counter.

C) MOD 128 ripple counter.

D) MOD 256 synchronous counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

5

Which group of logic devices represents the minimum hardware required for a MOD 64 synchronous counter?

A) five flip- flops, three AND gates

B) four flip- flops, two AND gates

C) six flip- flops, four AND gates

D) seven flip- flops, five AND gates

A) five flip- flops, three AND gates

B) four flip- flops, two AND gates

C) six flip- flops, four AND gates

D) seven flip- flops, five AND gates

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

6

The best way to eliminate decoding glitches in asynchronous counters is to:

A) use a strobe signal to disable the decoding AND gates until the flip- flops reach a stable state in response to a clock pulse.

B) use a strobe signal to disable the counter flip- flops until a time greater than N (tpd) has elapsed.

C) use a strobe signal to enable the decoding AND gates until the flip- flops reach a stable state in response to a clock pulse.

D) use a strobe signal to enable the counter flip- flops until a time greater than N (tpd) has elapsed.

A) use a strobe signal to disable the decoding AND gates until the flip- flops reach a stable state in response to a clock pulse.

B) use a strobe signal to disable the counter flip- flops until a time greater than N (tpd) has elapsed.

C) use a strobe signal to enable the decoding AND gates until the flip- flops reach a stable state in response to a clock pulse.

D) use a strobe signal to enable the counter flip- flops until a time greater than N (tpd) has elapsed.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

7

Synchronous (parallel) counters do not experience the delay problems encountered with asynchronous (ripple) counters because:

A) the input clock pulses are applied only to the last stage.

B) the input clock pulses are applied simultaneously to each stage.

C) the input clock pulses are not used to activate any of the counter stages.

D) the input clock pulses are applied only to the first and last stage.

A) the input clock pulses are applied only to the last stage.

B) the input clock pulses are applied simultaneously to each stage.

C) the input clock pulses are not used to activate any of the counter stages.

D) the input clock pulses are applied only to the first and last stage.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

8

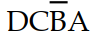

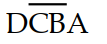

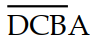

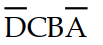

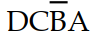

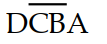

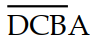

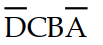

AND gates are being used to decode active- HIGH outputs from a MOD- 16 counter. An LED is to come on only when the count equals 1310. Assuming the D output is the MSB, the AND gate used to control the LED must have inputs of:

A)

B)

C)

D)

A)

B)

C)

D)

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

9

A common characteristic of ALL shift- register counters is:

A) they use fewer flip- flops than binary counters.

B) they require more decoding gates than do binary counters.

C) they all use feedback where the last flip- flop output is someway connected back to the first flip- flop.

D) they count in true binary form.

A) they use fewer flip- flops than binary counters.

B) they require more decoding gates than do binary counters.

C) they all use feedback where the last flip- flop output is someway connected back to the first flip- flop.

D) they count in true binary form.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

10

A primary advantage of using J- K flip- flops in asynchronous counter circuits is their ability to:

A) toggle on the clock if the J- K inputs are held HIGH.

B) toggle on the clock if the PRESET and CLEAR inputs are held LOW.

C) toggle on the clock if the PRESET and CLEAR inputs are held HIGH.

D) toggle on the clock if the J- K inputs are held LOW.

A) toggle on the clock if the J- K inputs are held HIGH.

B) toggle on the clock if the PRESET and CLEAR inputs are held LOW.

C) toggle on the clock if the PRESET and CLEAR inputs are held HIGH.

D) toggle on the clock if the J- K inputs are held LOW.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

11

A 30 kHz clock pulse is applied to a MOD- 15 ripple counter. What is the output frequency?

A) 2.5 kHz

B) 1.55 kHz

C) 2 kHz

D) 1.88 kHz

A) 2.5 kHz

B) 1.55 kHz

C) 2 kHz

D) 1.88 kHz

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

12

A MOD- 8 asynchronous counter has a "worst case" propagation delay of tphl = 37 ns. The maximum input clock frequency for this counter would be:

A) 6.756 MHz

B) 13.514 MHz

C) 9.009 MHz

D) 5.405 MHz

A) 6.756 MHz

B) 13.514 MHz

C) 9.009 MHz

D) 5.405 MHz

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

13

A synchronous MOD- 64 counter has tpd = 14 ns for each flip- flop and tpd = 12 ns for each AND gate. What is the maximum safe frequency for this counter?

A) 38.45 MHz

B) 83.33 MHz

C) 500 MHz

D) 71.43 MHz

A) 38.45 MHz

B) 83.33 MHz

C) 500 MHz

D) 71.43 MHz

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

14

Select the response that best defines the use of the Master Reset (MR) on typical counter ICs.

A) The MR is an asynchronous active HIGH input that resets the counter to the 00002 state.

B) The MR is an asynchronous active HIGH input that resets the counter to 00002 on the next clock pulse input.

C) The MR is a synchronous active HIGH J- K input that resets the counter to 00002.

D) The MR is a synchronous active HIGH input that resets the counter to 00002 on the next input clock pulse.

A) The MR is an asynchronous active HIGH input that resets the counter to the 00002 state.

B) The MR is an asynchronous active HIGH input that resets the counter to 00002 on the next clock pulse input.

C) The MR is a synchronous active HIGH J- K input that resets the counter to 00002.

D) The MR is a synchronous active HIGH input that resets the counter to 00002 on the next input clock pulse.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

15

How many AND gates would be required to completely decode all the states of a MOD- 64 counter and how many inputs must each AND gate have?

A) 128 gates, 5 inputs to each gate

B) 64 gates, 6 inputs to each gate

C) 64 gates, 5 inputs to each gate

D) 128 gates, 6 inputs to each gate

A) 128 gates, 5 inputs to each gate

B) 64 gates, 6 inputs to each gate

C) 64 gates, 5 inputs to each gate

D) 128 gates, 6 inputs to each gate

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

16

Asynchronous down counters:

A) require that the LSB flip- flop change states with each input clock pulse the same as an up counter.

B) require that the MSB and LSB flip- flops change states with each input clock pulse.

C) require that the MSB flip- flop change states with each input clock pulse the same as an up counter.

D) require that each flip- flop change states with each input clock pulse.

A) require that the LSB flip- flop change states with each input clock pulse the same as an up counter.

B) require that the MSB and LSB flip- flops change states with each input clock pulse.

C) require that the MSB flip- flop change states with each input clock pulse the same as an up counter.

D) require that each flip- flop change states with each input clock pulse.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

17

The type of counter where each flip- flop provides the CLK input to the next flip- flop is referred to as a_____counter.

A) Parallel

B) Ripple

C) Synchronous

D) Quadratic

A) Parallel

B) Ripple

C) Synchronous

D) Quadratic

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

18

The decoding gates for asynchronous counters may have "glitches" on their outputs because:

A) the flip- flops change states one at a time and erroneous counts may occur prior to the time all FF outputs have stabilized.

B) the flip- flops all change states at the same time but tpd may vary slightly for each FF thereby producing glitches.

C) the flip- flops change states one at a time; therefore no change for producing a glitch will ever exist.

D) the flip- flops all change states at the same time.

A) the flip- flops change states one at a time and erroneous counts may occur prior to the time all FF outputs have stabilized.

B) the flip- flops all change states at the same time but tpd may vary slightly for each FF thereby producing glitches.

C) the flip- flops change states one at a time; therefore no change for producing a glitch will ever exist.

D) the flip- flops all change states at the same time.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

19

A major advantage of the synchronous counter over the nonsynchronous counter is its ability to:

A) operate at lower frequencies.

B) operate with its J- K inputs tied permanently HIGH.

C) operate at higher frequencies.

D) operate with no external circuitry.

A) operate at lower frequencies.

B) operate with its J- K inputs tied permanently HIGH.

C) operate at higher frequencies.

D) operate with no external circuitry.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

20

A production plant needs a counter that will count 4,000 items before resetting and recycling. How many flip- flop stages would this counter require?

A) 12

B) 10

C) 13

D) 11

A) 12

B) 10

C) 13

D) 11

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

21

An asynchronous IC counter has clock inputs labeled  and https://d2lvgg3v3hfg70.cloudfront.net/TB9839/

and https://d2lvgg3v3hfg70.cloudfront.net/TB9839/ . The overbars indicate the clock inputs are activated by a:

. The overbars indicate the clock inputs are activated by a:

A) PGT.

B) NGT.

and https://d2lvgg3v3hfg70.cloudfront.net/TB9839/

and https://d2lvgg3v3hfg70.cloudfront.net/TB9839/ . The overbars indicate the clock inputs are activated by a:

. The overbars indicate the clock inputs are activated by a:A) PGT.

B) NGT.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

22

The asynchronous presetting of parallel counters to a specific count normally requires the use of the:

A) clock and the J- K inputs.

B) and the J- K inputs.

and the J- K inputs.

C) clock, PRESET, and CLEAR inputs.

D) 11eea480_e201_5074_97f4_27216f967a31_TB9839_11, PRESET, and CLEAR inputs.

A) clock and the J- K inputs.

B)

and the J- K inputs.

and the J- K inputs.C) clock, PRESET, and CLEAR inputs.

D) 11eea480_e201_5074_97f4_27216f967a31_TB9839_11, PRESET, and CLEAR inputs.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

23

How many stages would be required for a cascaded BCD counter to provide a decimal count of 9,999?

A) 5

B) 4

C) 3

D) 6

A) 5

B) 4

C) 3

D) 6

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

24

The highest stable count that a MOD 24 counter could produce would be:

A) 2310

B) 2410

C) 2510

D) 2610

A) 2310

B) 2410

C) 2510

D) 2610

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

25

A MOD 16 synchronous counter has inputs labeled , PO, P1, P2, and P3. These inputs would most probably be used to:

, PO, P1, P2, and P3. These inputs would most probably be used to:

A) reset the counter to 000O2 at the end of each count cycle.

B) reset the counter to 00002 anytime P0- P3 is active HIGH and 11eea480_e201_5074_97f4_27216f967a31_TB9839_11 is active LOW.

C) preset the counter to a value determined by the P0- P3 inputs anytime 11eea480_e201_5074_97f4_27216f967a31_TB9839_11 is active HIGH.

D) preset the counter to a value determined by the P0- P3 inputs anytime 11eea480_e201_5074_97f4_27216f967a31_TB9839_11 is active LOW.

, PO, P1, P2, and P3. These inputs would most probably be used to:

, PO, P1, P2, and P3. These inputs would most probably be used to:A) reset the counter to 000O2 at the end of each count cycle.

B) reset the counter to 00002 anytime P0- P3 is active HIGH and 11eea480_e201_5074_97f4_27216f967a31_TB9839_11 is active LOW.

C) preset the counter to a value determined by the P0- P3 inputs anytime 11eea480_e201_5074_97f4_27216f967a31_TB9839_11 is active HIGH.

D) preset the counter to a value determined by the P0- P3 inputs anytime 11eea480_e201_5074_97f4_27216f967a31_TB9839_11 is active LOW.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

26

A state transition diagram for designing a synchronous nonbinary counter should include:

A) the desired and the undesired states in any sequence.

B) the undesired states in their expected sequence as well as the desired in any sequence.

C) the desired states in any sequence and the undesired states in their expected sequence.

D) the desired states in the expected sequence as well as the undesired states leading to a desired state.

A) the desired and the undesired states in any sequence.

B) the undesired states in their expected sequence as well as the desired in any sequence.

C) the desired states in any sequence and the undesired states in their expected sequence.

D) the desired states in the expected sequence as well as the undesired states leading to a desired state.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

27

A MOD 12 and a MOD 10 counter are cascaded. The input clock frequency is 60 MHz. Determine the counter output frequency.

A) 1,500 kHz

B) 6 MHz

C) 5 MHz

D) 500 kHz

A) 1,500 kHz

B) 6 MHz

C) 5 MHz

D) 500 kHz

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

28

A basic principle of operation of the synchronous counter is:

A) The J- K inputs are connected so that J = 0, K = 1 so they can toggle on a specific clock pulse.

B) The J- K inputs are connected so that only those flip- flops that are supposed to toggle or a given clock pulse will have J = K = 1.

C) The J- K inputs are connected so that ALL flip- flops will have J - K = 1 so they can toggle on each input clock pulse.

D) The J = K inputs are connected so that every other flip- flop will have J = K = 1 so they can toggle on the input clock pulse.

A) The J- K inputs are connected so that J = 0, K = 1 so they can toggle on a specific clock pulse.

B) The J- K inputs are connected so that only those flip- flops that are supposed to toggle or a given clock pulse will have J = K = 1.

C) The J- K inputs are connected so that ALL flip- flops will have J - K = 1 so they can toggle on each input clock pulse.

D) The J = K inputs are connected so that every other flip- flop will have J = K = 1 so they can toggle on the input clock pulse.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

29

When designing a digital clock system using 60 Hz line frequency, the first two major stages should include:

A) a pulse shaper circuit and a BCD counter.

B) a pulse shaper circuit and a MOD 60 counter.

C) a MOD 60 counter and BCD counter.

D) a MOD 2 and BCD counter.

A) a pulse shaper circuit and a BCD counter.

B) a pulse shaper circuit and a MOD 60 counter.

C) a MOD 60 counter and BCD counter.

D) a MOD 2 and BCD counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

30

What type of register accepts data inputs one bit at a time and outputs all its data bits at the same time?

A) Parallel in/Parallel out

B) Serial in/Parallel out

C) Parallel in/Serial out

D) Serial in/Serial out

A) Parallel in/Parallel out

B) Serial in/Parallel out

C) Parallel in/Serial out

D) Serial in/Serial out

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

31

A parallel in/parallel out register normally has data inputs loaded and data outputs transferred ____.

A) asynchronously, asynchronously

B) synchronously, synchronously

C) synchronously, asynchronously

D) asynchronously, synchronously

A) asynchronously, asynchronously

B) synchronously, synchronously

C) synchronously, asynchronously

D) asynchronously, synchronously

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

32

Shift registers that are identified as parallel in/parallel out, serial in/parallel out, etc. are defined in this manner because:

A) it indicates the manner in which data are stored in the register.

B) it indicates the manner in which data can be entered into the register for storage and the manner in which data are outputted from the register.

C) it indicates the inverse of how data are entered into the register for storage and how data are outputted from the register.

D) Both A and C

A) it indicates the manner in which data are stored in the register.

B) it indicates the manner in which data can be entered into the register for storage and the manner in which data are outputted from the register.

C) it indicates the inverse of how data are entered into the register for storage and how data are outputted from the register.

D) Both A and C

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

33

Which of the following is TRUE regarding asynchronous counters?

A) propagation delay is increased

B) J and K inputs are permanently high on LSB flip- flop

C) less circuitry required than synchronous counters

D) J and K inputs must be decoded on the LSB

A) propagation delay is increased

B) J and K inputs are permanently high on LSB flip- flop

C) less circuitry required than synchronous counters

D) J and K inputs must be decoded on the LSB

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

34

A MOD- 32 synchronous counter requires:

A) 5 Flip- flops, 5 inverters, and 3 AND gates.

B) 4 Flip- flops, 2 AND gates, and 4 inverters.

C) 5 Flip- flops, 2 AND gates, and 3 inverters.

D) 5 Flip- flops 2 AND gates, and 4 inverters.

A) 5 Flip- flops, 5 inverters, and 3 AND gates.

B) 4 Flip- flops, 2 AND gates, and 4 inverters.

C) 5 Flip- flops, 2 AND gates, and 3 inverters.

D) 5 Flip- flops 2 AND gates, and 4 inverters.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

35

Karnaugh mapping is the preferred method to design logic circuits from an excitation diagram. Sum of product expressions can be formed directly from excitation tables. For J = X; K = X conditions:

A) do not form SOP expressions for X inputs.

B) X must be treated as a 0.

C) X must be treated as a 1.

D) any of the above

A) do not form SOP expressions for X inputs.

B) X must be treated as a 0.

C) X must be treated as a 1.

D) any of the above

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

36

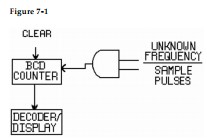

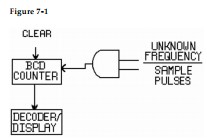

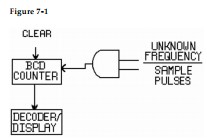

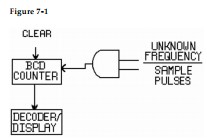

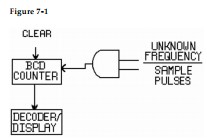

-Select the sequence for the counter in Figure 7- 1 that best describes its operation.

A) Counter clears: starts counting pulses when the sample pulse goes HIGH; stops counting when the sample pulse goes LOW. Clear pulse clears the counter by transferring its contents into the decoder/display unit.

B) Counter clears: starts counting pulses when the sampling pulse goes LOW; stops counting when the sampling pulse goes LOW; stops counting when the sample pulse goes LOW and displays the final count.

C) Counter clears: starts counting pulses when the sampling pulse goes HIGH; displays the counts as they occur and stop counting when the sampling pulse goes LOW. Count is displayed until the counter is cleared.

D) Counter clears: starts counting pulses when the sample pulse goes HIGH; stops counting when the sample pulse goes LOW. The LOW sample pulse activates the display and the final count is displayed.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

37

-What will the display reading in Figure 7- 1 be if the sampling interval is 100 ms and the unknown frequency is 200 kHz? (Assume the counter was cleared prior to the sampling interval.)

A) 15,000

B) 20,000

C) 5,000

D) 10,000

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

38

-A 4096 Hz signal is applied to the "unknown frequency" input in Figure 7- 1. The sampling interval is 20 ms. Determine the display reading after the sampling interval. (Assume the counter had been cleared prior to the sampling interval.)

A) 91 or 92

B) 101 or 102

C) 71 or 72

D) 81 or 82

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

39

-The "CLEAR" input in Figure 7- 1:

A) requires a HIGH input and is used as the initial clock pulse input for the counting operation.

B) requires a HIGH input and is used to clear the counter before the sampling interval begins.

C) requires a LOW input and is used to clear the counter before the sampling interval begins.

D) requires a LOW input and is used as the initial clock pulse for the counting operation.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

40

-The AND gate of Figure 7- 1 has a HIGH output only when:

A) an unknown frequency is present and the sample pulse input is LOW.

B) an unknown frequency input pulse is HIGH and the sample pulse input is HIGH.

C) the sample pulse input is HIGH and the unknown frequency input is LOW.

D) an unknown frequency is present.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

41

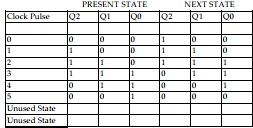

Table 7- 1  Table 7- 1 shows a state sequence used to program a GAL16V as a counter. The indicated sequence represents a:

Table 7- 1 shows a state sequence used to program a GAL16V as a counter. The indicated sequence represents a:

A) BCD counter.

B) Johnson counter.

C) ring counter.

D) binary counter.

Table 7- 1 shows a state sequence used to program a GAL16V as a counter. The indicated sequence represents a:

Table 7- 1 shows a state sequence used to program a GAL16V as a counter. The indicated sequence represents a:A) BCD counter.

B) Johnson counter.

C) ring counter.

D) binary counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

42

In asynchronous counters made of JK flip- flops, the main clock signal is fed into the CLK input of the most significant flip- flop.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

43

All decade counters are BCD counters.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

44

The propagation delay in individual stages of an asynchronous counter is cumulative.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

45

BCD counters usually have their count displayed on 7- segment displays.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

46

A counter whose MOD < 2N will have a 50% duty cycle.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

47

The MOD number of a Johnson counter always equals one- half the number of flip- flops in the counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

48

All flip- flops change states at the same time in an asynchronous counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

49

The + sign on a counter symbol by the input labeled CP indicates a count- up operation.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

50

Generally speaking, a synchronous counter requires more circuitry than a comparable asynchronous counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

51

The Q output from a JK flip- flop toggles on each clock input cycle as long as J = K = 1.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

52

A counter that counts from 0000 to 1111 is called a MOD- 16 counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

53

MOD number = 2n, where n = number of flip- flops.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

54

Typically, four flip- flops are required for a MOD- 60 counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

55

A MOD- 5 counter would count to a maximum of 101 and then clear to recycle.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

56

A MOD- 4 counter with an input clock frequency of 1500 Hz has an output frequency of 375 Hz.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

57

A MOD- 10 counter is also referred to as a decade counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

58

A MOD- 10 counter resets at 1010, thereby never actually reaching 10.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

59

One potential problem with asynchronous counters is that the overall propagation delay increases with each added flip- flop.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

60

Synchronous counters require less circuitry than asynchronous counters.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

61

An asynchronous, or____, counter is one where each FF output serves as the CLK

input source for the next FF.

input source for the next FF.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

62

For a pulse waveform, tw stands for ____.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

63

For any counter, the output from the last FF divides the input clock frequency by the____ number of the counter

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

64

The MOD- 10 counter is also referred to as a ____ counter.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

65

The megafunction LPM_SHIFTREG is found in the MegaWizard Manager's ____ folder.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

66

When two counters are cascaded, the overall MOD number is equal to the____of their individual MOD numbers

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

67

A reliable method for eliminating decoder spikes is to use a technique called____.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

68

Duty cycle is the ratio of ____ to____.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

69

____counters are often used whenever pulses are to be counted and the results are displayed in decimal.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

70

A single BCD counter counts from 0 to ____and then recycles to 0.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

71

When using the MegaWizard to design a counter, all you need to do is select the desired features, the number of bits, and the ____.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

72

Shift- register counters use____, which means that the output of the last FF in the register is connected back to the first FF in some way

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

73

The procedure to design sequences that cycle over and over begins by examination of a(n)____ table to understand the logic needed at the J and K inputs.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

74

A digital clock requires a clock input that cycles once each second ( f = 1 Hz). The 60 Hz line voltage can be processed through a Schmitt trigger and a ____ counter to provide the 1 Hz clock signal.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck

75

Data from a ____out 6- bit register could be loaded onto a data bus in one clock pulse.

Unlock Deck

Unlock for access to all 75 flashcards in this deck.

Unlock Deck

k this deck