Deck 8: Shift Registers

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Unlock Deck

Sign up to unlock the cards in this deck!

Unlock Deck

Unlock Deck

1/40

Play

Full screen (f)

Deck 8: Shift Registers

1

Shift registers are used primarily to store and transfer data.

True

2

A serial- in, serial- out shift register is used to transfer data one bit at a time from one line of a parallel bus to another.

False

3

The serial- in, parallel- out shift register is used to transfer data one bit at a time from one parallel data bus to another.

False

4

A parallel- in, serial- out shift register accepts all data bits simultaneously and transfers them out one bit at a time.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

5

Parallel- in, parallel- out registers have parallel input and output busses.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

6

Bidirectional shift registers can shift data either right or left.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

7

Shift register counters often include reset logic circuits that clear them after a desired count is reached.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

8

An effective time delay device can be constructed by using the propagation delay characteristics of a parallel shift register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

9

One method of troubleshooting sequential logic circuits involves a process of "exercising"

the circuit being tested with a known input waveform and then checking the output to see if the proper bit pattern is produced.

the circuit being tested with a known input waveform and then checking the output to see if the proper bit pattern is produced.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

10

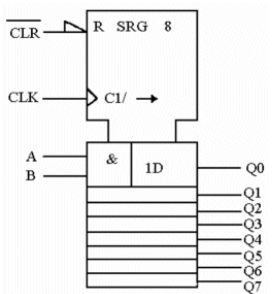

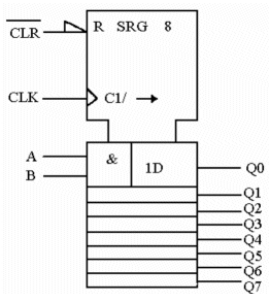

The top section of the 74164 serial- in, parallel- out shift register shown indicates that only the first DATA input section is controlled by the SRG 8 section.

?

?

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

11

What is the primary function of a register?

A) Decoding

B) Data storage (memory)

C) Encoding

D) Counting

A) Decoding

B) Data storage (memory)

C) Encoding

D) Counting

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

12

Which of the illustrations below represents the function of a parallel- in serial- out register?

A) Figure I.

B) Figure II.

C) Figure III.

D) Figure IV.

A) Figure I.

B) Figure II.

C) Figure III.

D) Figure IV.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

13

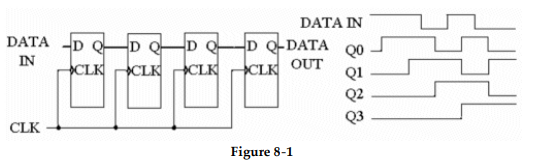

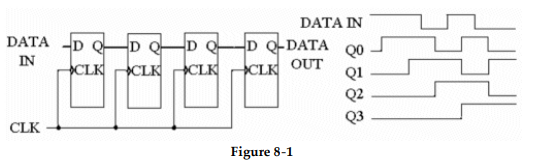

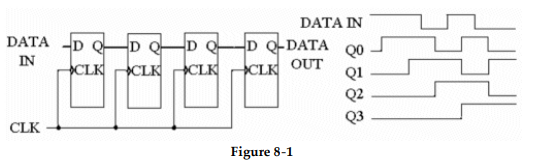

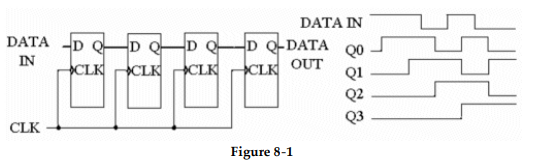

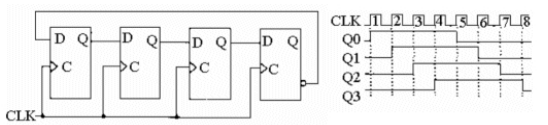

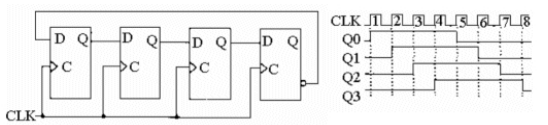

-How many data bits can be stored in the register shown in Figure 8- 1?

A) 2

B) 4

C) 32

D) 16

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

14

-How many clock cycles are required to enter a data group into the register in Figure 8- 1?

A) 32

B) 4

C) 16

D) 2

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

15

-After the DATA IN waveform in Figure 8- 1 is complete, what value is stored in the register?

A) 0 1 0 1

B) 1 0 1 0

C) 1 0 0 1

D) 1 1 0 1

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

16

-The circuit in Figure 8- 1 fails to produce the proper data output. The individual flip- flops are checked with a logic probe and pulser and each checks OK. What is the most likely cause of the problem?

A) The data output line is grounded.

B) One of the flip- flops has a solder bridge between its input and Vcc.

C) One of the interconnect lines between two stages has a solder bridge to ground.

D) One of the clock input lines is open.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

17

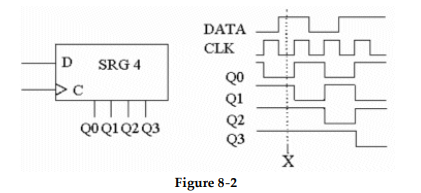

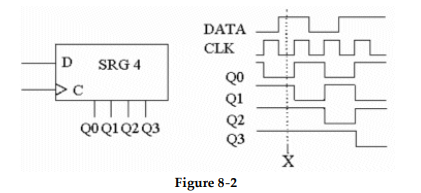

-Refer to the circuit and waveforms in Figure 8- 2. What value is stored in the register at the end of the fourth clock cycle?

A) 0 0 0 0

B) 0 1 1 0

C) 1 0 1 0

D) 0 1 0 1

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

18

-Refer to the circuit and waveforms in Figure 8- 2. What value is stored in the register at time 'X'?

A) 1 1 1 0

B) 0 1 0 1

C) 0 1 1 1

D) 0 1 1 0

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

19

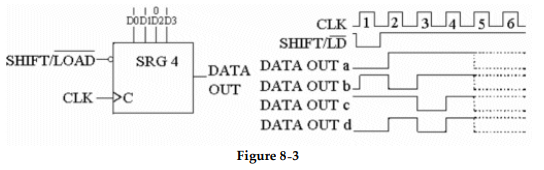

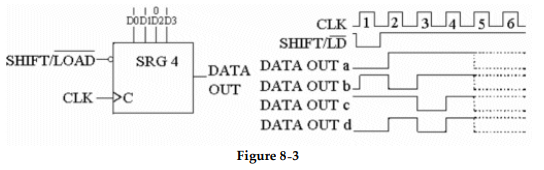

-The circuit shown in Figure 8- 3 is a_______.

A) demultiplexer

B) parallel- in serial- out register

C) serial- in parallel- load register

D) multiplexer

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

20

-Which of the DATA OUT waveforms shown in Figure 8- 3 is correct?

A) DATA OUT b.

B) DATA OUT c.

C) DATA OUT a.

D) DATA OUT d.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

21

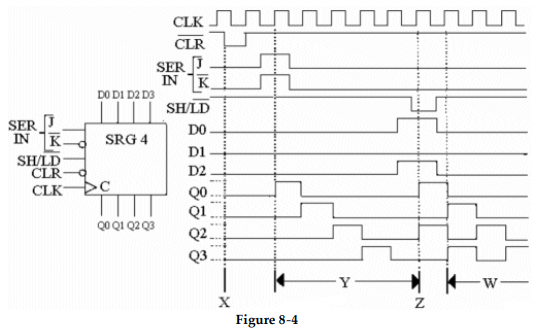

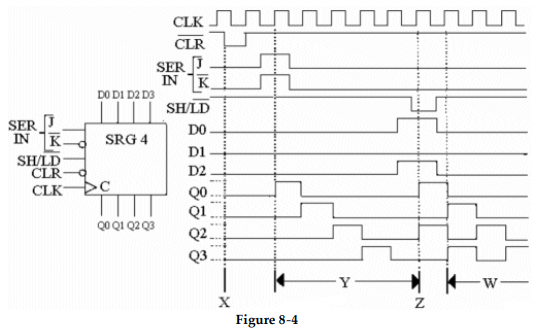

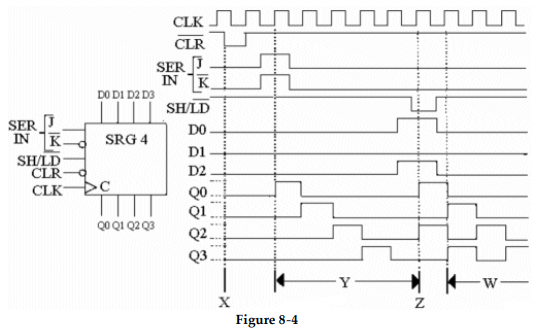

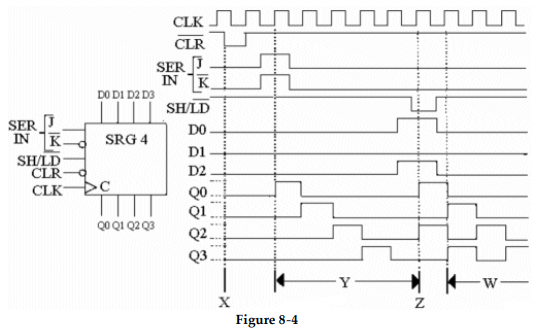

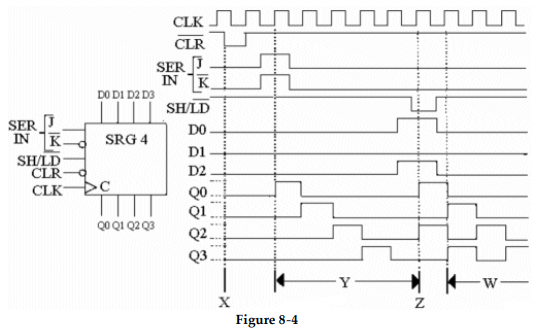

-What type of register is shown in Figure 8- 4?

A) Parallel- access shift register

B) Serial- in parallel- out register

C) Serial/parallel- in parallel- out register

D) Parallel- in parallel- out register

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

22

-Refer to Figure 8- 4. What occurs at point 'X' on the timing diagram?

A) The inputs will be disabled.

B) All inputs and outputs will be reset to LOW.

C) The outputs will all go LOW.

D) Only the CLK will be disabled during this time, preventing any transfer of data between inputs and outputs.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

23

-Refer to Figure 8- 4. What occurs during the time interval labeled 'Y'?

A) Clock pulses are toggled through the register.

B) Serial data is shifted through the register.

C) Parallel data transfer takes place.

D) Parallel data is shifted through the register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

24

-Refer to Figure 8- 4. What occurs at the point marked 'Z' on the timing diagram?

A) New serial data is loaded into the register.

B) The register is reset.

C) Parallel data is loaded into the register.

D) The register is placed into a holding state.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

25

-Refer to Figure 8- 4. What occurs during the interval marked 'W' on the timing diagram?

A) The data is shifted from the parallel inputs to the parallel outputs.

B) The register has just been cleared and the clock pulses are being toggled through the register.

C) Data is serially shifted through the register.

D) The register has gone into the counter mode and is counting the value of the parallel data previously stored on the parallel inputs.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

26

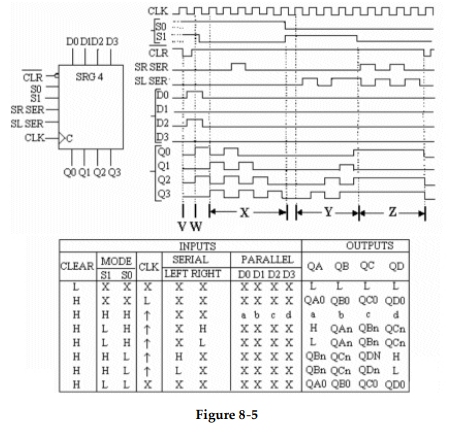

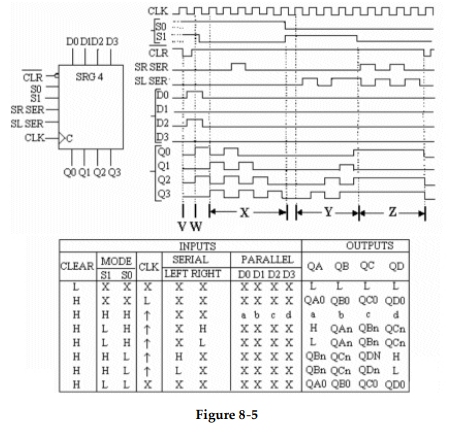

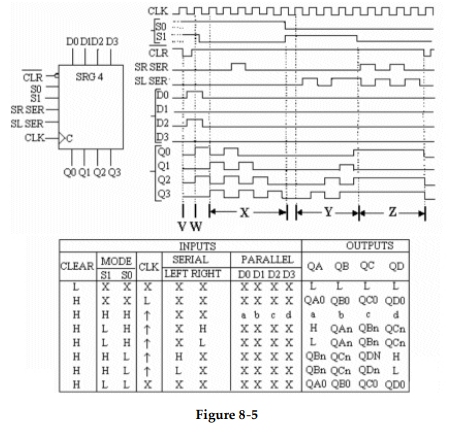

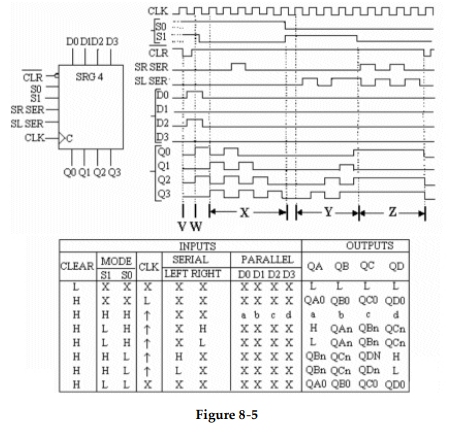

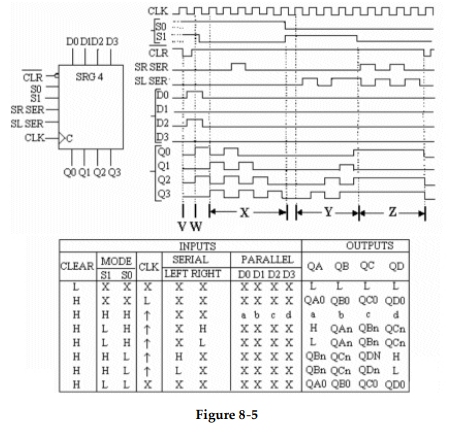

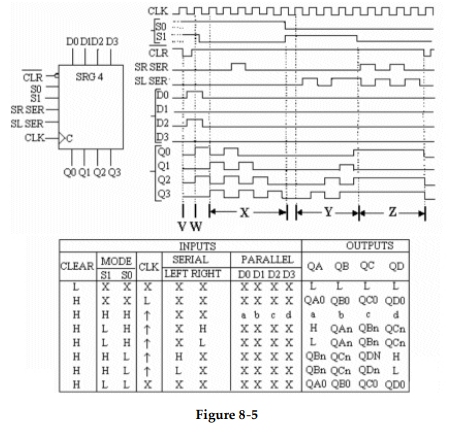

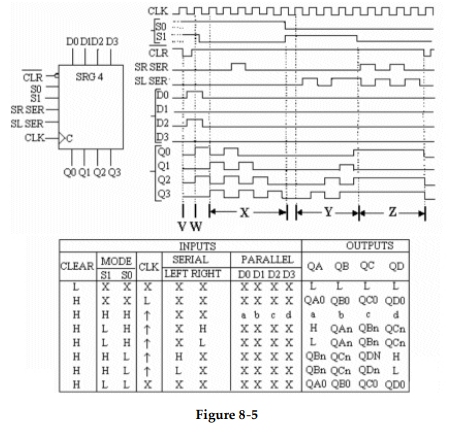

-What type of device is shown in Figure 8- 5?

A) Parallel- in parallel- out shift register with bidirectional data flow.

B) 4- bit bidirectional universal shift register.

C) 2- way parallel- in serial- out bidirectional register.

D) 2- bit serial- in 4- bit parallel- out bidirectional shift register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

27

-Refer to Figure 8- 5. What occurs at point 'V' on the timing diagram?

A) The outputs are cleared - set to LOW.

B) Data is loaded into the register from the parallel inputs.

C) The serial inputs are loaded into the register.

D) The parallel inputs are inhibited - prevented from loading into the register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

28

-Refer to Figure 8- 5. What occurs at point 'W' on the timing diagram?

A) Data is loaded into the register from the parallel inputs.

B) The parallel inputs are inhibited - prevented from loading into the register.

C) The outputs are cleared - set to LOW.

D) The serial inputs are loaded into the register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

29

-Refer to Figure 8- 5. What occurs during the interval labeled 'X' on the timing diagram?

A) Parallel data is entered into the register.

B) Data is shifted left through the register.

C) Data is shifted right through the register.

D) Serial data is entered into the register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

30

-Refer to Figure 8- 5. What occurs during the interval labeled 'Y' on the timing diagram?

A) Parallel data is entered into the register.

B) Serial data is entered into the register.

C) Data is shifted left through the register.

D) Data is shifted right through the register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

31

-Refer to Figure 8- 5. What occurs during the interval labeled 'Z' on the timing diagram?

A) Serial data is entered into the register.

B) Data is shifted left through the register.

C) The operation of the register is inhibited-no changes occur on the outputs.

D) Data is shifted right through the register.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

32

-Refer to the Function Table in Figure 8- 5. What occurs if the CLEAR, S1 and S0 inputs all go HIGH?

A) The parallel registers are RESET and the serial data inputs are inhibited.

B) The parallel data inputs are loaded and passed to the parallel data outputs.

C) The operation of the register is inhibited.

D) The exact response depends on the values that are loaded into the parallel data inputs.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

33

In order to use a shift register as a counter, _________.

A) the register's serial input is the counter input and the serial output is the counter output

B) a serial- in, serial- out register must be used

C) the input is applied to the parallel inputs and the output is taken from the serial data output

D) the serial output of the register is connected back to its serial input

A) the register's serial input is the counter input and the serial output is the counter output

B) a serial- in, serial- out register must be used

C) the input is applied to the parallel inputs and the output is taken from the serial data output

D) the serial output of the register is connected back to its serial input

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

34

Which of the following is a shift register counter?

A) Binary

B) Ring

C) BCD

D) Decade

A) Binary

B) Ring

C) BCD

D) Decade

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

35

The circuit shown below is a _______.

A) Johnson counter

B) decade counter

C) BCD counter

D) ring counter

A) Johnson counter

B) decade counter

C) BCD counter

D) ring counter

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

36

What is the modulus of a 6- stage Johnson counter?

A) 64

B) 12

C) 6

D) 32

A) 64

B) 12

C) 6

D) 32

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

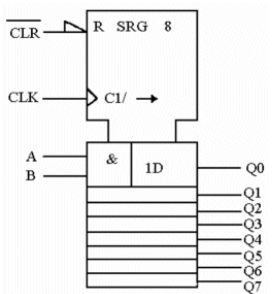

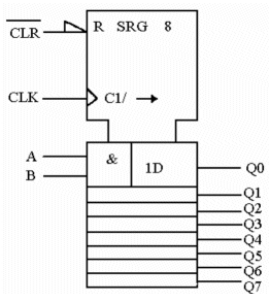

37

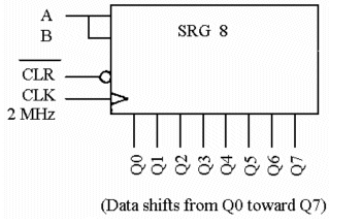

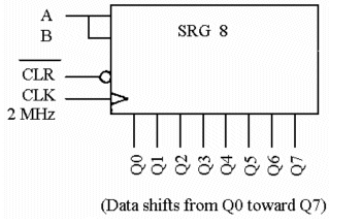

A serial data path needs a 2000 ns delay. Which output from the circuit below will provide the correct delay?

A) Q1

B) Q7

C) Q0

D) Q3

A) Q1

B) Q7

C) Q0

D) Q3

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

38

What does UART stand for, and what does it do?

A) Universal ASCII Receiver Transmitter; it is used to transmit and receive ASCII characters.

B) United Artists Radio and Television; the standard data interfacing system first used by the movie industry.

C) Universal ASCII Relay Transmission; defines a method (standard) by which data communications can be made between parallel and serial devices or systems.

D) Universal Asynchronous Receiver Transmitter; it is used to interface the parallel data bus in a typical computer system to serial data transmission lines.

A) Universal ASCII Receiver Transmitter; it is used to transmit and receive ASCII characters.

B) United Artists Radio and Television; the standard data interfacing system first used by the movie industry.

C) Universal ASCII Relay Transmission; defines a method (standard) by which data communications can be made between parallel and serial devices or systems.

D) Universal Asynchronous Receiver Transmitter; it is used to interface the parallel data bus in a typical computer system to serial data transmission lines.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

39

A technician is testing an undocumented digital system with a signature analyzer. What indications should the technician look for?

A) Without documented signatures, the instrument is basically useless.

B) Look for similar signatures that show up at different points in the circuit; no two points should be the same.

C) As signals flow from one circuit to another, changes will take place; look for changes in the signatures, especially between inputs and outputs.

D) Use a logic analyzer to verify the correct operation of the signature analyzer; once its accuracy has been confirmed, its indications can be relied upon for troubleshooting.

A) Without documented signatures, the instrument is basically useless.

B) Look for similar signatures that show up at different points in the circuit; no two points should be the same.

C) As signals flow from one circuit to another, changes will take place; look for changes in the signatures, especially between inputs and outputs.

D) Use a logic analyzer to verify the correct operation of the signature analyzer; once its accuracy has been confirmed, its indications can be relied upon for troubleshooting.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

40

When using an oscilloscope to troubleshoot a digital system, the instrument should be triggered by_________.

A) line sync, in order to observe troublesome power line glitches

B) the AC line voltage

C) the A channel or channel 1

D) the system clock

A) line sync, in order to observe troublesome power line glitches

B) the AC line voltage

C) the A channel or channel 1

D) the system clock

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck