Deck 15: Integrated Circuit Technologies

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Question

Unlock Deck

Sign up to unlock the cards in this deck!

Unlock Deck

Unlock Deck

1/40

Play

Full screen (f)

Deck 15: Integrated Circuit Technologies

1

The nominal value of the dc supply voltage for TTL devices is +3.3V.

False

2

The noise margin for TTL is 0.8V.

False

3

The average power dissipation for TTL can be calculated using PD = VCCICC.

True

4

Propagation delay time is the time delay between an input signal causing an output signal.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

5

The data sheet for the 74 series of TTL ICs shows that VCC has a range of 4.5 V to 5.5 V.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

6

Most TTL gates contain a totem- pole output circuit.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

7

The term open- drain means that the drain terminal of the output transistor is not internally connected to the supply voltage.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

8

The TTL HIGH level source current is higher than the LOW level sinking current.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

9

CMOS circuits utilize enhancement- mode MOSFETs.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

10

The fanout of CMOS gates is frequency dependent.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

11

Due to the extremely low power requirements of CMOS logic circuits, any number of CMOS and TTL gates can be interconnected.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

12

ECL gates are noted for their high frequency capability and low- amplitude output voltage.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

13

NMOS devices use MOSFETs to implement the full range of logic functions using the universal NAND gate.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

14

The LOW logic level for standard TTL input cannot exceed _________.

A) 0.4V.

B) 5V.

C) 0.8V.

D) 0.0V.

A) 0.4V.

B) 5V.

C) 0.8V.

D) 0.0V.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

15

The HIGH logic level for a standard TTL output must be at least _________V.

A) 2.4

B) 0.8

C) 5

D) 2

A) 2.4

B) 0.8

C) 5

D) 2

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

16

Propagation delay is important because _________.

A) it limits the maximum operating frequency of a gate

B) the logic gates must be given a short break during each clock cycle or else they will overheat

C) it is a measure of how long the clock must be applied to the gate before it will make the required decision

D) all the gates in a system must have the same propagation times in order to be compatible

A) it limits the maximum operating frequency of a gate

B) the logic gates must be given a short break during each clock cycle or else they will overheat

C) it is a measure of how long the clock must be applied to the gate before it will make the required decision

D) all the gates in a system must have the same propagation times in order to be compatible

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

17

Why is the fanout of CMOS gates frequency dependent?

A) The higher the number of gates attached to the output, the more frequently they will have to be serviced, thus reducing the frequency at which each will be serviced with an input signal.

B) Each CMOS input gate has a specific propagation time and this limits the number of different gates that can be connected to the output of a CMOS gate.

C) When the frequency reaches the critical value, the gate will only be capable of delivering 70% of the normal output voltage and consequently the output power will be one- half of normal; this defines the upper operating frequency.

D) The input gates of the FETs are predominantly capacitive, and as the signal frequency increases the capacitive loading also increases, thereby limiting the number of loads that may be attached to the output of the driving gate.

A) The higher the number of gates attached to the output, the more frequently they will have to be serviced, thus reducing the frequency at which each will be serviced with an input signal.

B) Each CMOS input gate has a specific propagation time and this limits the number of different gates that can be connected to the output of a CMOS gate.

C) When the frequency reaches the critical value, the gate will only be capable of delivering 70% of the normal output voltage and consequently the output power will be one- half of normal; this defines the upper operating frequency.

D) The input gates of the FETs are predominantly capacitive, and as the signal frequency increases the capacitive loading also increases, thereby limiting the number of loads that may be attached to the output of the driving gate.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

18

As more load gates are connected to a driving gate, the loading on the driving gate _________.

A) decreases

B) increases

C) serves as a current sink

D) serves as a current source

A) decreases

B) increases

C) serves as a current sink

D) serves as a current source

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

19

Which of the following will not normally be found on a data sheet?

A) Maximum LOW level output voltage

B) Minimum LOW level output voltage

C) Maximum HIGH level input current

D) Minimum HIGH level output voltage

A) Maximum LOW level output voltage

B) Minimum LOW level output voltage

C) Maximum HIGH level input current

D) Minimum HIGH level output voltage

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

20

What are the major differences between the 5400 and 7400 series of ICS?

A) The 7400 series was originally developed by Texas Instruments; the 5400 series was brought out by National Semiconductors after TI's patents expired, as a second supply source.

B) The 7400 series are an improvement over the original 5400s.

C) The 5400 series are military grade and require tighter supply voltages and temperatures.

D) The 5400 series are military grade and allow for a wider range of supply voltage and temperatures.

A) The 7400 series was originally developed by Texas Instruments; the 5400 series was brought out by National Semiconductors after TI's patents expired, as a second supply source.

B) The 7400 series are an improvement over the original 5400s.

C) The 5400 series are military grade and require tighter supply voltages and temperatures.

D) The 5400 series are military grade and allow for a wider range of supply voltage and temperatures.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

21

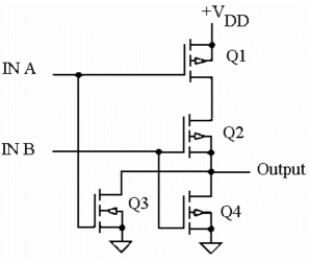

?

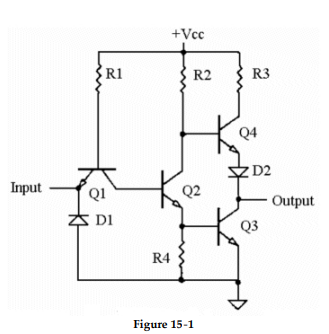

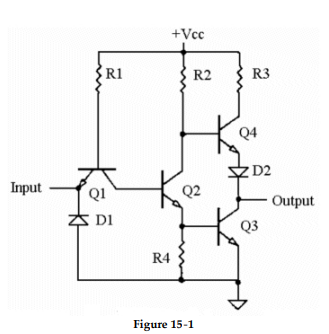

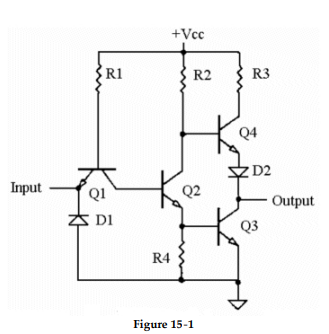

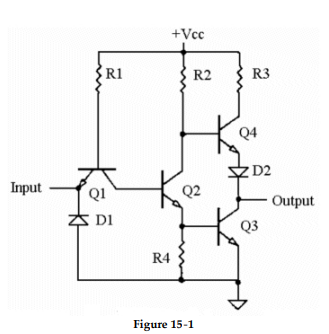

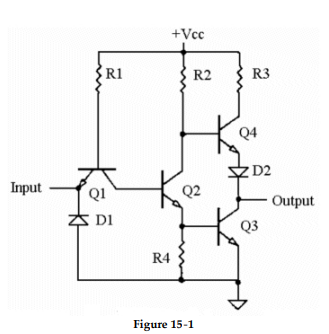

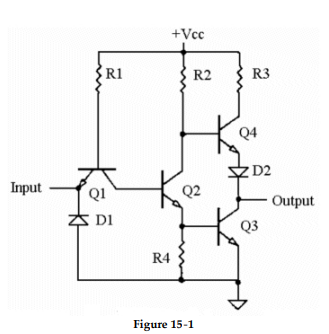

-Refer to Figure 15- 1. Which of the following describes the operation of the circuit?

A) A LOW input turns Q1 and Q4 off, Q2 and Q3 are on.

B) A HIGH input turns Q1, Q2 and Q4 on; and Q3 is off.

C) A HIGH input turns Q1, Q2 and Q3 off, and Q4 on.

D) A LOW input turns Q1 and Q3 on; Q2 and Q4 are off.

-Refer to Figure 15- 1. Which of the following describes the operation of the circuit?

A) A LOW input turns Q1 and Q4 off, Q2 and Q3 are on.

B) A HIGH input turns Q1, Q2 and Q4 on; and Q3 is off.

C) A HIGH input turns Q1, Q2 and Q3 off, and Q4 on.

D) A LOW input turns Q1 and Q3 on; Q2 and Q4 are off.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

22

?

-Refer to Figure 15- 1. What is the output transistor configuration called?

A) Quasi push- pull

B) Push- pull

C) Complementary- symmetry

D) Totem- Pole

-Refer to Figure 15- 1. What is the output transistor configuration called?

A) Quasi push- pull

B) Push- pull

C) Complementary- symmetry

D) Totem- Pole

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

23

?

-What functions do D1 and D2 serve in Figure 15- 1?

A) D1 clamps the input of Q1 to prevent saturation, and D2 prevents reverse voltage spikes from damaging Q4.

B) D1 and D2 are both steering diodes which are used to ensure that the input current is correctly steered to the proper output terminal.

C) D1 provides a return path for the emitter current of Q1, and D2 prevents reverse voltage from being applied to Q3.

D) D1 prevents negative spikes from damaging Q1, and D2 ensures that Q4 will be off when Q2 is on.

-What functions do D1 and D2 serve in Figure 15- 1?

A) D1 clamps the input of Q1 to prevent saturation, and D2 prevents reverse voltage spikes from damaging Q4.

B) D1 and D2 are both steering diodes which are used to ensure that the input current is correctly steered to the proper output terminal.

C) D1 provides a return path for the emitter current of Q1, and D2 prevents reverse voltage from being applied to Q3.

D) D1 prevents negative spikes from damaging Q1, and D2 ensures that Q4 will be off when Q2 is on.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

24

?

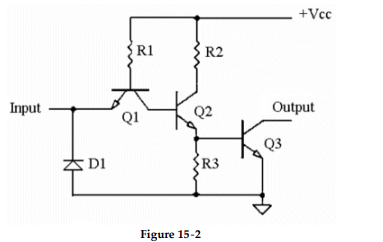

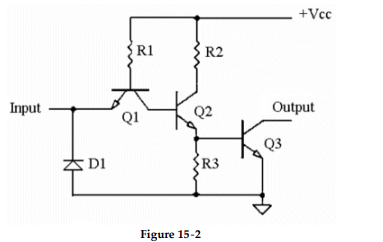

-What type of circuit is shown in Figure 15- 2, and how is the output ordinarily connected?

A) It is an open- collector gate. An external load must be connected between the output terminal and an appropriate supply voltage terminal.

B) It represents an active- LOW inverter and is used in negative logic systems.

C) It is an open- collector gate and is used to drive loads that cannot be connected directly to Vcc due to high noise levels.

D) Any of the above could be correct, depending on the specific application involved.

-What type of circuit is shown in Figure 15- 2, and how is the output ordinarily connected?

A) It is an open- collector gate. An external load must be connected between the output terminal and an appropriate supply voltage terminal.

B) It represents an active- LOW inverter and is used in negative logic systems.

C) It is an open- collector gate and is used to drive loads that cannot be connected directly to Vcc due to high noise levels.

D) Any of the above could be correct, depending on the specific application involved.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

25

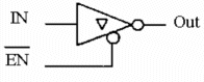

What type of circuit is represented below?

A) It is an active LOW buffer.

B) It is a programmable inverter.

C) It is a tristate inverter.

D) None of the above is correct.

A) It is an active LOW buffer.

B) It is a programmable inverter.

C) It is a tristate inverter.

D) None of the above is correct.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

26

What is unique about 74SXX- series TTL devices?

A) The S denotes a slow version of the device, which is a consequence of its higher power rating.

B) The gate transistors are silicon (S), and the gates therefore have lower values of leakage current.

C) The S denotes the fact that a single gate is present in the IC rather than the usual package of 2- 6 gates.

D) The devices use Schottky transistors and diodes to prevent them from going into saturation; this results in faster turn on and turn off times, which translates into higher frequency operation.

A) The S denotes a slow version of the device, which is a consequence of its higher power rating.

B) The gate transistors are silicon (S), and the gates therefore have lower values of leakage current.

C) The S denotes the fact that a single gate is present in the IC rather than the usual package of 2- 6 gates.

D) The devices use Schottky transistors and diodes to prevent them from going into saturation; this results in faster turn on and turn off times, which translates into higher frequency operation.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

27

When the output of a standard TTL gate is HIGH, it can __________.

A) sink a maximum of 400- microamps from a maximum of 10 load gates

B) source 400- microamps of current to a maximum of 10 attached gates

C) source 16mA of current to a maximum of 10 attached gates

D) sink 16mA of current from the attached input gates

A) sink a maximum of 400- microamps from a maximum of 10 load gates

B) source 400- microamps of current to a maximum of 10 attached gates

C) source 16mA of current to a maximum of 10 attached gates

D) sink 16mA of current from the attached input gates

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

28

Totem- pole outputs_________.

A) cannot be connected together because high currents can damage one or both of the transistors if the outputs are in opposite states (one HIGH and one LOW)

B) can be connected together to handle higher load currents and output voltages

C) can be connected in parallel when higher output currents are required

D) can be connected in series when higher output voltages are required

A) cannot be connected together because high currents can damage one or both of the transistors if the outputs are in opposite states (one HIGH and one LOW)

B) can be connected together to handle higher load currents and output voltages

C) can be connected in parallel when higher output currents are required

D) can be connected in series when higher output voltages are required

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

29

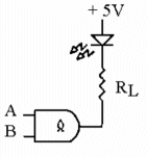

What type of device is shown below and what input levels are required to turn the LED off?

A) The device is an open- collector AND gate and requires both inputs to be HIGH in order to turn the LED off.

B) The device is a Schottky open- collector AND gate and requires a low on both inputs to turn the LED off.

C) The device is an open- collector AND gate and requires only one low input to turn the LED off.

D) The device is a Schottky AND gate and requires only one low input to turn the LED off.

A) The device is an open- collector AND gate and requires both inputs to be HIGH in order to turn the LED off.

B) The device is a Schottky open- collector AND gate and requires a low on both inputs to turn the LED off.

C) The device is an open- collector AND gate and requires only one low input to turn the LED off.

D) The device is a Schottky AND gate and requires only one low input to turn the LED off.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

30

What should be done to unused inputs on TTL gates?

A) All unused inputs should be connected to an unused output; this will insure compatible loading on both the unused inputs and unused outputs.

B) All unused gates should be connected together and tied to Vcc through a 1k- ohm resistor.

C) They should be left disconnected so as not to produce a load on any of the other circuits and to minimize power loading on the voltage source.

D) Unused AND and NAND inputs should be tied to Vcc through a 1k- ohm resistor; unused OR and NOR inputs should be grounded.

A) All unused inputs should be connected to an unused output; this will insure compatible loading on both the unused inputs and unused outputs.

B) All unused gates should be connected together and tied to Vcc through a 1k- ohm resistor.

C) They should be left disconnected so as not to produce a load on any of the other circuits and to minimize power loading on the voltage source.

D) Unused AND and NAND inputs should be tied to Vcc through a 1k- ohm resistor; unused OR and NOR inputs should be grounded.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

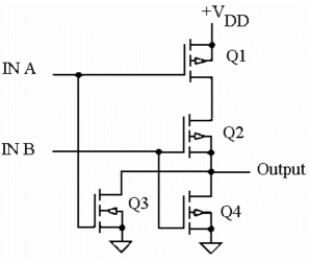

31

What type of logic circuit is shown below?

A) It is a PMOS NAND gate.

B) It is a NMOS AND gate.

C) It is a CMOS AND gate.

D) It is a CMOS NOR gate.

A) It is a PMOS NAND gate.

B) It is a NMOS AND gate.

C) It is a CMOS AND gate.

D) It is a CMOS NOR gate.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

32

Which of the following statements apply to CMOS devices?

A) The devices should be stored and shipped in antistatic tubes or conductive foam.

B) The devices should not be inserted into circuits with the power on.

C) All tools, test equipment and metal workbenches should be tied to earth ground.

D) All of the above are correct.

A) The devices should be stored and shipped in antistatic tubes or conductive foam.

B) The devices should not be inserted into circuits with the power on.

C) All tools, test equipment and metal workbenches should be tied to earth ground.

D) All of the above are correct.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

33

Which of the following logic families has the highest noise margin?

A) CMOS

B) LS TTL

C) TTL

D) HCMOS

A) CMOS

B) LS TTL

C) TTL

D) HCMOS

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

34

Which of the following logic families has the highest maximum clock frequency?

A) S- TTL

B) AS- TTL

C) HCMOS

D) HS- TTL

A) S- TTL

B) AS- TTL

C) HCMOS

D) HS- TTL

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

35

Which of the following logic families has the shortest propagation delay?

A) HCMOS

B) HS- TTL

C) AS- TTL

D) S- TTL

A) HCMOS

B) HS- TTL

C) AS- TTL

D) S- TTL

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

36

Which of the following accurately describes ECL?

A) ECL stands for energy- coupled logic; the input energy is amplified by the input transistors and allows the device to deliver higher output currents.

B) ECL stands for emitter- coupled logic; all of the emitters of the input transistors are connected together and each transistor functions as an emitter follower.

C) ECL stands for emitter- coupled logic; all of the inputs are coupled into the device through the emitters of the input transistors.

D) ECL stands for electron- coupled logic; all of the devices used within the gates are N- type transistors.

A) ECL stands for energy- coupled logic; the input energy is amplified by the input transistors and allows the device to deliver higher output currents.

B) ECL stands for emitter- coupled logic; all of the emitters of the input transistors are connected together and each transistor functions as an emitter follower.

C) ECL stands for emitter- coupled logic; all of the inputs are coupled into the device through the emitters of the input transistors.

D) ECL stands for electron- coupled logic; all of the devices used within the gates are N- type transistors.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

37

Which of the following summarizes the important features of ECL?

A) Low noise margin, low output voltage swing, negative voltage operation, fast, and high power consumption.

B) Poor noise immunity, positive supply voltage operation, good low frequency operation, and low power.

C) Good noise immunity, negative logic, high frequency capability, low power dissipation and short propagation time.

D) Slow propagation time, high frequency response, low power consumption, and high output voltage swings.

A) Low noise margin, low output voltage swing, negative voltage operation, fast, and high power consumption.

B) Poor noise immunity, positive supply voltage operation, good low frequency operation, and low power.

C) Good noise immunity, negative logic, high frequency capability, low power dissipation and short propagation time.

D) Slow propagation time, high frequency response, low power consumption, and high output voltage swings.

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

38

Which of the logic families listed below allows the highest operating frequency?

A) HCMOS

B) ECL

C) 74AS

D) 54S

A) HCMOS

B) ECL

C) 74AS

D) 54S

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

39

PMOS and NMOS _________.

A) represent MOSFET devices utilizing either p- channel or n- channel devices exclusively within a given gate

B) represent positive and negative MOS type devices which can be operated from differential power supplies and are compatible with operational amplifiers

C) are enhancement type CMOS devices used to produce a series of high- speed logic known as 74HC

D) none of the above are correct

A) represent MOSFET devices utilizing either p- channel or n- channel devices exclusively within a given gate

B) represent positive and negative MOS type devices which can be operated from differential power supplies and are compatible with operational amplifiers

C) are enhancement type CMOS devices used to produce a series of high- speed logic known as 74HC

D) none of the above are correct

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck

40

Which of the following logic families has the best noise immunity?

A) ALS

B) DTL

C) HCMOS

D) TTL

A) ALS

B) DTL

C) HCMOS

D) TTL

Unlock Deck

Unlock for access to all 40 flashcards in this deck.

Unlock Deck

k this deck