The Essentials Of Computer Organization And Architecture 4th Edition by Linda Null,Julia Lobur

Edition 4ISBN: 978-1284074482

The Essentials Of Computer Organization And Architecture 4th Edition by Linda Null,Julia Lobur

Edition 4ISBN: 978-1284074482 Exercise 20

Assuming the same stages as in Example 5.12, explain the potential pipeline hazards (if any) in each of the following code segments.

Reference of Example 5.12:

Suppose we have a 4-stage pipeline, where:

• S1 = fetch instruction

• S2 = decode and calculate effective address

• S3 = fetch operand

• S4 = execute instruction and store results

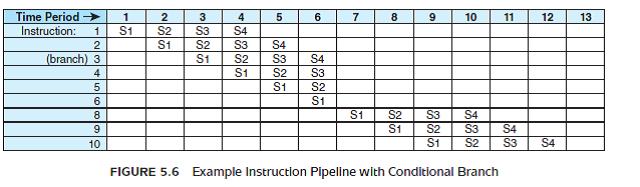

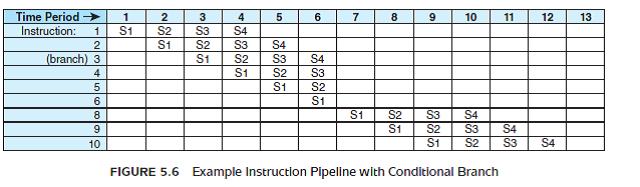

We must also assume that the architecture provides a means to fetch data and instructions in parallel. This can be done with separate instruction and data paths; however, most memory systems do not allow this. Instead, they provide the operand in cache, which, in most cases, allows the instruction and operand to be fetched simultaneously. Suppose, also, that instruction I3 is a conditional branch statement that alters the execution sequence (so that instead of I4 running next, it transfers control to I8). This results in the pipeline operation shown in Figure 5.6.

Note that I4, I5, and I6 are fetched and proceed through various stages, but after the execution of I3 (the branch), I4, I5, and I6 are no longer needed. Only after time period 6, when the branch has executed, can the next instruction to be executed (I8) be fetched, after which the pipe refills. From time periods 6 through 9, only one instruction has executed. In a perfect world, for each time period after the pipe originally fills, one instruction should flow out of the pipeline. However, we see in this example that this is not necessarily true.

Reference of Example 5.12:

Suppose we have a 4-stage pipeline, where:

• S1 = fetch instruction

• S2 = decode and calculate effective address

• S3 = fetch operand

• S4 = execute instruction and store results

We must also assume that the architecture provides a means to fetch data and instructions in parallel. This can be done with separate instruction and data paths; however, most memory systems do not allow this. Instead, they provide the operand in cache, which, in most cases, allows the instruction and operand to be fetched simultaneously. Suppose, also, that instruction I3 is a conditional branch statement that alters the execution sequence (so that instead of I4 running next, it transfers control to I8). This results in the pipeline operation shown in Figure 5.6.

Note that I4, I5, and I6 are fetched and proceed through various stages, but after the execution of I3 (the branch), I4, I5, and I6 are no longer needed. Only after time period 6, when the branch has executed, can the next instruction to be executed (I8) be fetched, after which the pipe refills. From time periods 6 through 9, only one instruction has executed. In a perfect world, for each time period after the pipe originally fills, one instruction should flow out of the pipeline. However, we see in this example that this is not necessarily true.

Explanation

a) X=R2+Y

R4=R2+X

Here, these two instru...

The Essentials Of Computer Organization And Architecture 4th Edition by Linda Null,Julia Lobur

Why don’t you like this exercise?

Other Minimum 8 character and maximum 255 character

Character 255