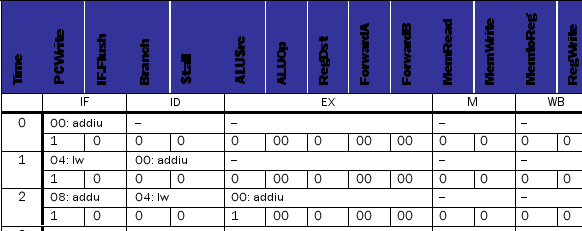

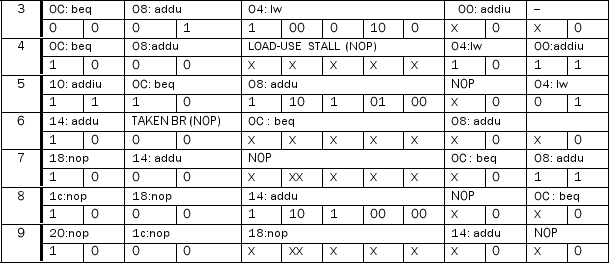

Consider the datapath below. This machine does not support code with branch delay slots. (It predicts not-taken with a 1-cycle penalty on taken branches.) For each control signal listed in the table below, determine its value at cycles 3 through 9, inclusive. Also, show the instruction occupying each stage of the pipeline in all cycles. (Assume the IF/ID write-enable line is set to the inverse of the Stall signal.)

The initial state of the machine is:

PC = 0

All pipeline registers contain 0s

All registers in the register file contain 0s. The data memory contains 0s in all locations The instruction memory contains:

00: addiu $3, $zero, 4 04: lw $4, 100($3)

08: addu $2, $4, $3

0C: beq $4, $zero, 0x14 10: addiu $3, $3, 1

14: addu $2, $2, $3

all other locations contain 0

Use data forwarding whenever possible. All mux inputs are numbered vertically from "top" to "bottom" starting at 0 as you look at the datapath in the proper landscape orientation. Also, the values for ALUOp are:

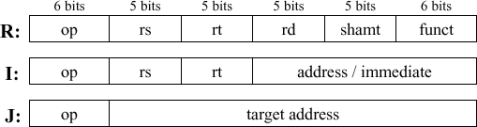

Instruction formats:

Instruction formats:

Correct Answer:

Verified

Q7: The classic 5-stage pipeline seen in Section

Q8: A two-part question.

-(Part A) Dependence detection

This question

Q9: A two-part question.

-Given four instructions, how many

Q10: Pipelining is used because it improves instruction

Q11: You are given a 4-stage pipelined

Q13: Structural, data and control hazards typically require

Q14: This is a three-part question about critical

Q15: Consider the following data path diagram:

Q16: Branch Prediction. Consider the following sequence of

Q17: Forwarding logic design. For this problem you

Unlock this Answer For Free Now!

View this answer and more for free by performing one of the following actions

Scan the QR code to install the App and get 2 free unlocks

Unlock quizzes for free by uploading documents